W

WA microprocessor is a computer processor that is implemented on a single integrated circuit (IC) of MOSFET construction. The microprocessor is a multipurpose, clock-driven, register-based, digital integrated circuit that accepts binary data as input, processes it according to instructions stored in its memory, and provides results as output. Microprocessors contain both combinational logic and sequential digital logic. Microprocessors operate on numbers and symbols represented in the binary number system.

W

W W

WTRIPS was a microprocessor architecture designed by a team at the University of Texas at Austin in conjunction with IBM, Intel, and Sun Microsystems. TRIPS uses an instruction set architecture designed to be easily broken down into large groups of instructions (graphs) that can be run on independent processing elements. The design collects related data into the graphs, attempting to avoid expensive data reads and writes and keeping the data in high speed memory close to the processing elements. The prototype TRIPS processor contains 16 such elements. TRIPS hoped to reach 1 TFLOP on a single processor, as papers were published from 2003 to 2006.

W

WThe 1801 series CPUs were a family of 16-bit Soviet microprocessors based on the indigenous Elektronika NC microarchitecture cores, but binary compatible with DEC's PDP-11 machines. First released in 1980, various models and variants of the series were among the most popular Soviet microprocessors and dominated embedded systems and military applications of the 1980s. They were also used in widely different areas such as graphing calculators and industrial CNCs, but arguably their most well-known use was in several Soviet general-purpose mini- and microcomputer designs like the SM EVM, DVK, UKNC, and BK families. Due to being the CPU of the popular Elektronika BK home computer, used in its late years as a demo machine, as well as the DVK micros that often offered a first glimpse into the UNIX world, this processor achieved something of a cult status among Soviet and then Russian programmers.

W

WApple-designed processors, marketed for the Macintosh as Apple silicon, are system on a chip (SoC) and system in a package (SiP) processors designed by Apple Inc., mainly using the ARM architecture. They are the basis of Apple's iPhone, iPad, and Apple Watch platforms, and of products such as the HomePod, iPod touch, and Apple TV. Apple also designs a SoC called the Apple H1 for its AirPods line of wireless headphones. On June 22, 2020, at WWDC 2020, Apple announced plans to switch its Macintosh computers from Intel processors to ARM-based, Apple-designed processors. The first of the ARM-based Macs, using the Apple M1 processor, were announced on November 10, 2020.

W

WBaikal CPU is a line of MIPS and ARM-based microprocessors developed by fabless design firm Baikal Electronics, a spin-off of the Russian supercomputer company T-Platforms.

W

WThe Clipper architecture is a 32-bit RISC-like instruction set architecture designed by Fairchild Semiconductor. The architecture never enjoyed much market success, and the only computer manufacturers to create major product lines using Clipper processors were Intergraph and High Level Hardware. The first processors using the Clipper architecture were designed and sold by Fairchild, but the division responsible for them was subsequently sold to Intergraph in 1987; Intergraph continued work on Clipper processors for use in its own systems.

W

WElbrus-2S+ is a multi-core microprocessor based on the Elbrus 2000 architecture developed by Moscow Center of SPARC Technologies (MCST) There are multiple reports regarding the evolution of this technology for the purpose of import substitution in Russia, which was raised by several ministries on July 2014, due to economic sanctions in response to 2014 pro-Russian unrest in Ukraine. In December 2014, it was announced that Mikron start pilot production of a dual-core variant of this microprocessor called Elbrus-2SM using a 90 nanometer CMOS manufacturing process in Zelenograd, Russia.

W

WThe Elbrus-8S is a Russian 28 nanometer 8-core microprocessor developed by Moscow Center of SPARC Technologies (MCST). The first prototypes were produced by the end of 2014 and serial production started in 2016. The Elbrus-8S is to be used in servers and workstations. The processor's architecture allows support of up to 32 processors on a single server motherboard.

W

WThe EnCore microprocessor family is a configurable and extendable implementation of a compact 32-bit RISC instruction set architecture - developed by the PASTA Research Group at the University of Edinburgh School of Informatics. The following are key features of the EnCore microprocessor family:5 stage pipeline highest operating frequency in its class lowest possible dynamic energy consumption - 99% of flip-flops automatically clock-gated using typical synthesis tools most non-memory operations achieving single-cycle latency, and no more than one load-delay slot easy configurability of cache architectures compact baseline instruction set architecture (ISA), including freely-mixed 16-bit and 32-bit encodings for maximum code density no overhead for switching between 16- and 32-bit instruction encodings

W

WThe Fairchild F8 is an 8-bit microprocessor system created by Fairchild Semiconductor announced in 1974, shipped in 1975.

W

WThe 6309 is Hitachi's CMOS version of the Motorola 6809 microprocessor. While in "Emulation Mode" it is fully compatible with the 6809. To the 6809 specifications it adds higher clock rates, enhanced features, new instructions, and additional registers. Most new instructions were added to support the additional registers, as well as up to 32-bit math, hardware division, bit manipulations, and block transfers. The 6309 is generally 30% faster in native mode than the 6809.

W

WIGNITE is a stack-based RISC microprocessor architecture. The architecture was originally developed by Nanotronics, which was later acquired by Patriot Scientific Corporation. The IGNITE microprocessor is one of the few commercially produced microprocessors that use a stack-based computation model. Target applications for this unique architecture were primarily embedded devices as well as efficient implementation of virtual stack machines, such as the Java Virtual Machine or the stack machine underlying the Forth programming language. The IGNITE processor was never successful in the market.

W

WThe Intersil 6100 is a single-chip microprocessor implementation of the 12-bit PDP-8 instruction set, along with a range of peripheral support and memory ICs developed by Intersil in the mid-1970s. It was sometimes referred to as the CMOS-PDP8. Since it was also produced by Harris Corporation, it was also known as the Harris HM-6100. The Intersil 6100 was introduced in the second quarter of 1975, and the Harris version in 1976.

W

WThe K1810VM86 is a Soviet 16-bit microprocessor, a clone of the Intel 8086 CPU with which it is binary and pin compatible. It was developed between 1982 and 1985. The original K1810VM86 supported a clock frequency of up to 5 MHz while up to 8 MHz were allowed for the later K1810VM86M. The K1810VM86 was manufactured plastic 40-pin dual in-line package or in a 40-pin ceramic dual in-line package. A clone of the related Intel 8088 with its 8-bit bus was manufactured as the K1810VM88, also in plastic and ceramic packages.

W

WThe KR580VM80A is a Soviet microprocessor, a clone of the Intel 8080 CPU. Different versions of this CPU were manufactured beginning in the late 1970s, the earliest known use being in the SM1800 computer in 1979. Initially called the K580IK80 (К580ИК80), it was produced in a 48-pin planar metal-ceramic package. Later, a version in a PDIP-40 package was produced and was named the KR580IK80A (КР580ИК80А). The pin layout of the latter completely matched that of Intel's 8080A CPU. In 1986 this CPU received a new part number to conform with the 1980 Soviet integrated circuit designation and became known as the KR580VM80A (КР580ВМ80А), the number it is most widely known by today. Normal clock frequency for the K580IK80A is 2 MHz, with speeds up to 2.5 MHz for the KR580VM80A. The KR580IK80A was manufactured in a 6 µm process. In the later KR580VM80A the feature size was reduced to 5 µm and the die became 20% smaller.

W

WMali-400 MP is a Mali series GPU produced by ARM Holdings.

W

WThe MaverickCrunch is a floating point math coprocessor core intended for digital audio. It was first presented by Cirrus Logic in June 2000 together with an ARM920T integer processor in their 200 MHz EP9302 EP9307 EP9312 and EP9315 System-on-Chip integrated circuits. Plagued with hardware bugs and poor compiler support, it was seldom used in any of the devices based on those chips and the product line was discontinued on April 1, 2008.

W

WThe MCST R1000 is a 64-bit microprocessor developed by Moscow Center of SPARC Technologies (MCST) and fabricated by TSMC.

W

WIn computer engineering, microarchitecture, also called computer organization and sometimes abbreviated as µarch or uarch, is the way a given instruction set architecture (ISA) is implemented in a particular processor. A given ISA may be implemented with different microarchitectures; implementations may vary due to different goals of a given design or due to shifts in technology.

W

WMMN80CPU is a Z80A microprocessor clone, working at 3.5 MHz. It was produced from 1988 onwards at Microelectronica Bucharest for Romanian 8 bit computers such as HC, CIP, JET, TIM-S, CoBra and others.

W

WMorse Micro is a Sydney-based developer of Wi-Fi HaLow microprocessors. The chips use low-bandwidth wireless network protocols in the sub 1 GHz spectrum, enabling high data rates of 10 megabits per second, at a range of 1,000 metres. The Australian Government provided them with seed funding in 2017 as they believed Morse Micro has the “first WiFi HaLow silicon chip that securely connects smart devices over long distances.” The company says the main application of their technology is machine-to-machine communications, which is “expanding Wi-Fi so it can go into everything, every smoke alarm, every camera." In May 2019, Series A funding was provided in by a suite of investors including the CSIRO Innovation Fund, part of the Australian scientific research agency credited with inventing Wi-Fi in 1997.

W

WA multi-core processor is a computer processor on a single integrated circuit with two or more separate processing units, called cores, each of which reads and executes program instructions. The instructions are ordinary CPU instructions but the single processor can run instructions on separate cores at the same time, increasing overall speed for programs that support multithreading or other parallel computing techniques. Manufacturers typically integrate the cores onto a single integrated circuit die or onto multiple dies in a single chip package. The microprocessors currently used in almost all personal computers are multi-core.

W

WMultiClet is an ongoing innovation project for a microprocessor that claims to be the first post von Neumann, multicellular microprocessor, breaking the paradigm for computing technology that has been in place for more than 60 years. There have been attempts in the past to shift away from the von Neumann architecture, but no one has really taken it to the limit by trying to implement a fully multicellular - dynamically reconfigurable microprocessor. Now 4-cellular dynamically reconfigurable microprocessor is implemented.

W

WIn computer architecture, multithreading is the ability of a central processing unit (CPU) to provide multiple threads of execution concurrently, supported by the operating system. This approach differs from multiprocessing. In a multithreaded application, the threads share the resources of a single or multiple cores, which include the computing units, the CPU caches, and the translation lookaside buffer (TLB).

W

WNational Semiconductor's IPC-16A/520 PACE, short for "Processing and Control Element", was the first commercial single-chip 16-bit microprocessor. PACE had four general-purpose accumulators, with an instruction set architecture loosely based on the earlier IMP-16 architecture, which in turn had been inspired by the Data General Nova minicomputer.

W

WNEC V60 was a CISC microprocessor manufactured by NEC starting in 1986. It has a memory management unit (MMU), and real-time operating system (RTOS) support for both Unix-based user-application-oriented systems and for I‑TRON–based hardware-control-oriented embedded systems. This article also describes the V70 and V80, as these share the same instruction set architecture (ISA) with the V60. In addition, a dedicated co-FPP, multi-cpu lockstep fault-tolerant mechanism named FRM, development tools including Ada certified system MV‑4000, and in-circuit emulator (ICE) are described. Their successor, the V800 Series product families, are briefly introduced.

W

WThe R800 is the central processing unit used in the MSX Turbo-R home computer. The R800 was designed by ASCII Corporation of Japan and built by Mitsui & Co., Ltd.. The goal was a modern and pipelined CPU binary compatible with the Z80, and therefore with MSX software, while also maintaining compatibility with older MSX Z80-based hardware.

W

WSHAKTI is the first open-source initiative by the Reconfigurable Intelligent Systems Engineering (RISE) group at Indian Institute of Technology, Madras to develop the first indigenous industrial-grade processor. The aim of SHAKTI initiative includes building an opensource production-grade processor, complete System on Chips (SoCs), development boards and SHAKTI based software platform. The primary focus of the team is architecture research to develop SoCs, which is competitive with commercial offerings in the market concerning area, power and performance. All the source codes for SHAKTI are open-sourced under the Modified BSD License of the University of California, Berkeley. The project was funded by Ministry of Electronics and Information Technology (MeITY), Government of India.

W

WThe 8X300 is a microprocessor produced and marketed by Signetics starting 1976 as a second source for the SMS 300 by Scientific Micro Systems, Inc.

W

WThe Signetics 2650 was an 8-bit microprocessor introduced in mid-1975. According to Adam Osborne's book An Introduction to Microprocessors Vol 2: Some Real Products, it was "the most minicomputer-like" of the microprocessors available at the time. A combination of missing features and odd memory access limited its appeal, and the system saw little use in the market. Signetics became better known as a second-source supplier for the MOS 6502.

W

WTensor Processing Unit (TPU) is an AI accelerator application-specific integrated circuit (ASIC) developed by Google specifically for neural network machine learning, particularly using Google's own TensorFlow software. Google began using TPUs internally in 2015, and in 2018 made them available for third party use, both as part of its cloud infrastructure and by offering a smaller version of the chip for sale.

W

WThe Crusoe is a family of x86-compatible microprocessors developed by Transmeta and introduced in 2000. Crusoe was notable for its method of achieving x86 compatibility. Instead of the instruction set architecture being implemented in hardware, or translated by specialized hardware, the Crusoe runs a software abstraction layer, or a virtual machine, known as the Code Morphing Software (CMS). The CMS translates machine code instructions received from programs into native instructions for the microprocessor. In this way, the Crusoe can emulate other instruction set architectures (ISAs).

W

WThe Efficeon processor is Transmeta's second-generation 256-bit VLIW design released in 2004 which employs a software engine to convert code written for x86 processors to the native instruction set of the chip. Like its predecessor, the Transmeta Crusoe, Efficeon stresses computational efficiency, low power consumption, and a low thermal footprint.

W

WThe transputer is a series of pioneering microprocessors from the 1980s, featuring integrated memory and serial communication links, intended for parallel computing. They were designed and produced by Inmos, a semiconductor company based in Bristol, United Kingdom.

W

WThe U880 is an 8-bit microprocessor that was manufactured by VEB Mikroelektronik "Karl Marx" Erfurt in the German Democratic Republic. Production of the U880 started in 1980 at VEB Funkwerk Erfurt. The U880 is an unlicensed clone of the Zilog Z80 microprocessor. It is not, however, a direct copy of the Zilog's Z80. Differences include not setting the CY flag for the OUTI command.

W

WThe U80601 was a 16-bit microprocessor made in 1989-1990 by Kombinat Mikroelektronik Erfurt in the former German Democratic Republic of East Germany. It was manufactured in NMOS technology and encased in a PLCC or ceramic (CLCC) package.

W

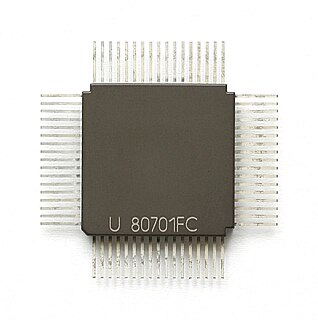

WThe U80701 was a 32-bit microprocessor developed from 1986-1990 in the German Democratic Republic. It was manufactured by VEB Mikroelektronik "Karl Marx" Erfurt (MME) in NMOS technology and encased in a ceramic quad flat package.

W

WUltra-low-voltage processors are a class of microprocessor that are deliberately underclocked to consume less power, at the expense of performance.